# FPGA Lecture for LUPO and GTO Vol. 1 2010, 31 August (revised 2013, 19 November) H. Baba

#### Contents

- Basic feature of FPGA

- Basic usage for LUPO

- New project

- Read and Write

- Basic behavioral VHDL simulation

- Download firmware

#### What is FPGA ?

#### Field Programmable Gate Array

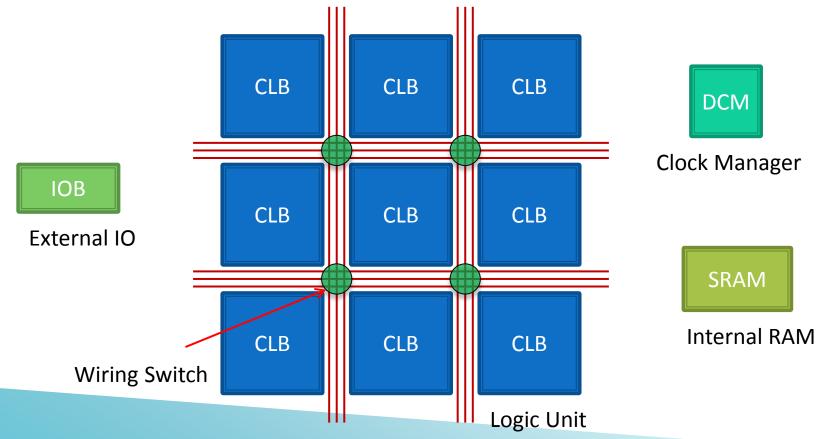

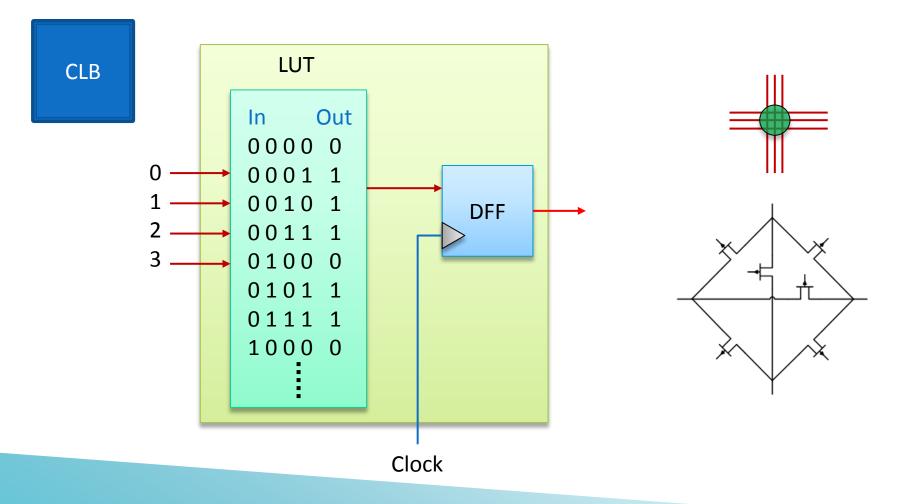

# CLB and wiring

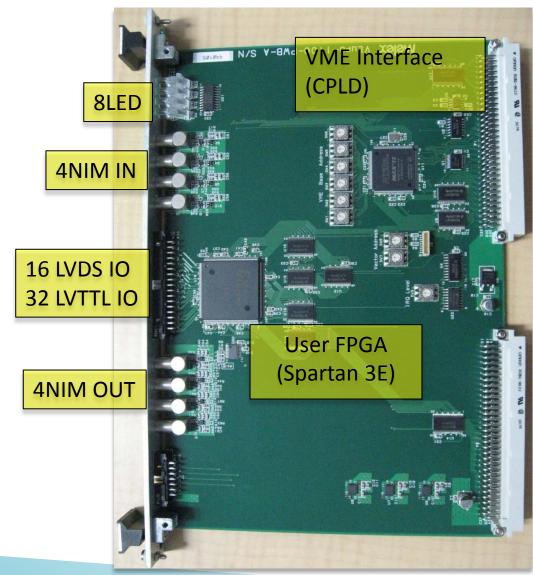

# About LUPO

- NIM signals are converted to LVTTL

- NIM->LVTTL->FPGA

- FPGA->LVTTL->NIM

- LVDS ports are direct connection

- Because of this IOB is 2.5V, this port can be accept 2.5V

IO signals

## New Project for LUPO

#### Device and Design flow

| Property Name                          | Value               |   |  |  |  |  |  |

|----------------------------------------|---------------------|---|--|--|--|--|--|

| Product Category                       | All                 |   |  |  |  |  |  |

| Family                                 | Spartan3E           |   |  |  |  |  |  |

| Device                                 | XC3S500E            | ~ |  |  |  |  |  |

| Package                                | PQ208               | ~ |  |  |  |  |  |

| Speed                                  | -4                  | ~ |  |  |  |  |  |

| Top-Level Source Type                  | HDL                 | V |  |  |  |  |  |

| Synthesis Tool                         | XST (VHDL/Verilog)  | ~ |  |  |  |  |  |

| Simulator                              | ISim (VHDL/Verilog) | ~ |  |  |  |  |  |

| Preferred Language                     | VHDL                | ~ |  |  |  |  |  |

| Property Specification in Project File | Store all values    | ~ |  |  |  |  |  |

| Manual Compile Order                   |                     |   |  |  |  |  |  |

| VHDL Source Analysis Standard          | VHDL-93             | ~ |  |  |  |  |  |

|                                        |                     |   |  |  |  |  |  |

| Enable Message Filtering               |                     |   |  |  |  |  |  |

## Design property for GTO

| <u>P</u> roject Settings               |                          |

|----------------------------------------|--------------------------|

| Property Name                          | Value                    |

| Top-Level Source Type                  | HDL                      |

|                                        |                          |

| Evaluation Development Board           | None Specified           |

| Product Category                       | All                      |

| Family                                 | Spartan3A and Spartan3AN |

| Device                                 | XC3S200A                 |

| Package                                | VQ100                    |

| Speed                                  | -4                       |

|                                        |                          |

| Synthesis Tool                         | XST (VHDL/Verilog)       |

| Simulator                              | ISim (VHDL/Verilog)      |

| Preferred Language                     | VHDL                     |

| Property Specification in Project File | Store all values         |

| Manual Compile Order                   |                          |

| VHDL Source Analysis Standard          | VHDL-93                  |

|                                        |                          |

| Enable Message Filtering               |                          |

|                                        | OK Cancel Help           |

# The definition of IO (LUPO)

- LED : LED

- A : CAMAC/VME address

- CLOCK : 50MHz clock

- ▶ INIT : CAMAC Z/C, VME Init?

- IP : NIM Input 0-3

IP0 : IP0 to GCLK

- OP : NIM Output 0-3

- LVDSn/LVDSp : LVDS IO 0-15

- LVDS\_CLKn/p : LVDS0 to GCLK

- RD : Data Read

- WR : Data Write

- RD\_STRB : Read strobe

- WR\_STRB : Write strobe

```

entity HOGE is

port (

: out STD LOGIC VECTOR (7 downto 0);

LED

LVDS CLKn : in

STD LOGIC;

LVDS CLKp : in

STD LOGIC;

LVDSn

: in STD LOGIC VECTOR (15 downto 0);

: in STD LOGIC VECTOR (15 downto 0);

LVDSp

: out STD LOGIC VECTOR (15 downto 0);

LVDSn

: out STD LOGIC VECTOR (15 downto 0);

LVDSp

: in STD LOGIC VECTOR (7 downto 0);

А

CLOCK

STD LOGIC;

: in

INIT

: in

STD LOGIC;

IPO

: in STD LOGIC;

STD LOGIC VECTOR (3 downto 0);

IΡ

: in

: in STD LOGIC VECTOR (3 downto 0);

UDI

UDO

: out STD LOGIC VECTOR (3 downto 0);

: out STD LOGIC;

IRQ

: out STD LOGIC VECTOR (3 downto 0);

OP

RD

: out STD LOGIC VECTOR (31 downto 0);

STD LOGIC VECTOR (31 downto 0);

WR

: in

: in

STD LOGIC;

RD STRB

WR STRB

: in

STD LOGIC);

end HOGE;

```

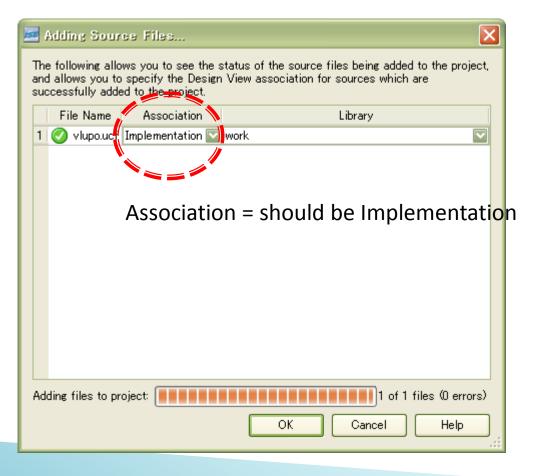

# Copy the Constraint file (UCF)

- vlupo.ucf

- gto.ucf

- Write constraints for IO and others

# Without CAMAC/VME Buses (LUPO)

#### This is enough

```

entity HOGE is

port (

LED : out STD_LOGIC_VECTOR (7 downto 0);

CLOCK : in STD_LOGIC;

IP : in STD_LOGIC_VECTOR (3 downto 0);

OP : out STD_LOGIC_VECTOR (3 downto 0));

end HOGE;

```

#### NETs written in UCF are must be written in "entity" also

#### Edit vlupo.ucf by "Edit Constraints(Text)"

| NET  | "CLOCK"   | LOC = "P177"   IOSTANDARD = LVTTL ;       |   |

|------|-----------|-------------------------------------------|---|

| NET  | "IP[0]"   | LOC = "P202"   IOSTANDARD = LVTTL ;       |   |

| NET  | "IP[1]"   | LOC = "P203"   IOSTANDARD = LVTTL ;       |   |

| NET  | "IP[2]"   | LOC = "P204"   IOSTANDARD = LVTTL ;       |   |

| NET  | "IP[3]"   | LOC = "P205"   IOSTANDARD = LVTTL ;       |   |

| NET  | "IRQ" LO  | OC = "P64"   IOSTANDARD = LVCMOS25 ;      |   |

| NET  | "LED[0]"  | LOC = "P189"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[1]"  | LOC = "P190"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[2]"  | LOC = "P192"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[3]"  | LOC = "P193"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[4]"  | LOC = "P196"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[5]"  | LOC = "P197"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[6]"  | LOC = "P199"   IOSTANDARD = LVTTL ;       |   |

| NET  | "LED[7]"  | LOC = "P200"   IOSTANDARD = LVTTL ;       |   |

| NET  | "OP[0]"   | LOC = "P63"   IOSTANDARD = LVCMOS25 ;     |   |

| NET  | "OP[1]"   | LOC = "P62"   IOSTANDARD = LVCMOS25 ;     |   |

| NET  | "OP[2]"   | LOC = "P61"   IOSTANDARD = LVCMOS25 ;     |   |

| NET  | "OP[3]"   | LOC = "P60"   IOSTANDARD = LVCMOS25 ;     |   |

| NET  | "CLOCK"   | <pre>TNM_NET = CLOCK;</pre>               |   |

| TIME | ESPEC "TS | _CLOCK" = PERIOD "CLOCK" 20 ns HIGH 50 %; | ; |

|      |           |                                           |   |

# Simple case (LUPO)

#### Like this

```

architecture Behavioral of HOGE is

begin

OP(0) <= IP(0) and IP(1);

OP(1) <= IP(2) or IP(3);

OP(2) <= IP(0) and not IP(1);

OP(3) <= CLOCK;

LED(3 downto 0) <= IP(3 downto 0);

LED(7 downto 4) <= (others => '1');

```

```

architecture Behavioral of HOGE is

signal a, b, c : std_logic;

begin

a <= IP(0) and IP(1);

b <= IP(2) or IP(3);

c <= a and not b;

OP(0) <= a;

OP(1) <= b;

OP(2) <= c;

OP(3) <= CLOCK;

LED(3 downto 0) <= IP(3 downto 0);

LED(7 downto 4) <= (others => '1');

```

If Synthesize -> Implement Design are passed, it will work

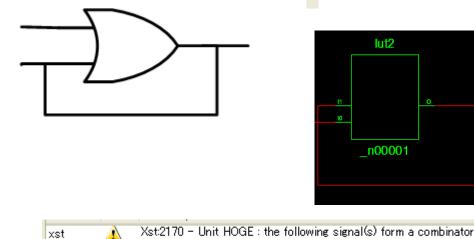

## To make the synchronous circuit

- When you use "if, else", you should put values into all signals explicitly

- Check Warning

|   |    | ldc |  |   |  |

|---|----|-----|--|---|--|

| D |    |     |  | ٩ |  |

|   |    |     |  |   |  |

| G |    |     |  |   |  |

| C | LR |     |  |   |  |

| d |    |     |  |   |  |

In this case, created circuit will be asynchronous circuit

```

process(IP(0), IP(1))

begin

if(IP(0) = '1') then

d <= '0';

e <= '1';

elsif(IP(1) = '1') then

d <= '1';

e <= '0';

Should write

else

d <= '0';

values in "else"

e <= '0';

end if:

explicitly

end process;

```

Xst:737 - Found 1-bit latch for signal <d>. Latches may be generated from incomplete case or if statements. We do not recommend the use of latches in FPGA/CPLD designs, as they may lead to timing problems.

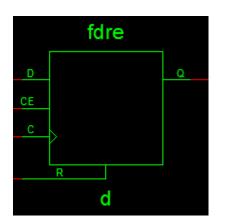

## This type works well, usually

By using "event process", DFF will be used, and values are kept as you had expected

Values are changed at the Clock timing

```

signal d, e : std_logic := '0';

begin

process(CLOCK)

begin

if(CLOCK'event and CLOCK='1') then

if(IP(0) = '1') then

d <= '1';

e <= '1';

e <= '1';

else

d <= '0';

--            e <= '0';

end if;

end if;

end process;

```

### Basically, all lines run in parallel

```

OP(0) <= d;

OP(1) <= e;

OP(2) <= '0';

OP(3) <= '0';

process (CLOCK)

begin

if(CLOCK'event and CLOCK='1') then

if(IP(0) = '1') then

d <= '1';

e <= d;

else

d <= '0';

e <= d;

end if;

end if;

end process;

```

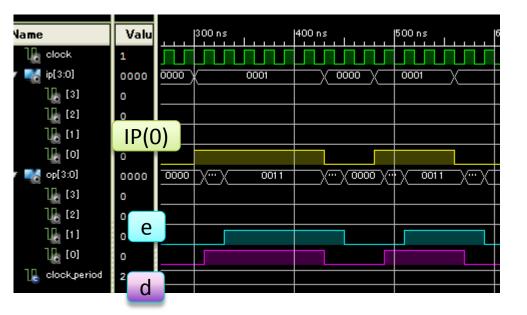

## Be careful about the loop circuit

As this schematic, you can make the "Latch circuit", but...  $a \ll IP(0)$  or a;

Xst:2170 - Unit HOGE : the following signal(s) form a combinatorial loop:

- Warnings of Combinational loop

- It will not work, depending on the pulse width, line delay, jitter and so on

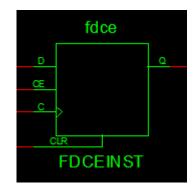

# Expressly using FF is safe

- "event" in the process statement makes DFF, basically

- As a circuit component, if you use FDCE(=DFF), it will work as you expected

COMPONENT FDCE generic (INIT : bit := '1'); PORT ( Q : OUT std logic; С : IN std logic; : IN std logic; CLR : IN std logic; : IN std logic); END COMPONENT: signal a : std logic; begin --a <= IP(0) or a; FDCEINST: FDCE generic map( INIT => '0') PORT MAP( => a, => IP(0), CE => '1', CLR => '0', => '1' D ); OP(0) <= a;

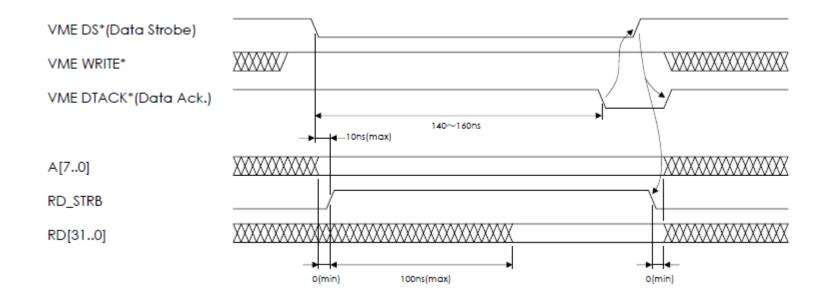

#### Accessing VME/CAMAC buses (Read for LUPO)

```

Latch data during RD_STRB = '1'

```

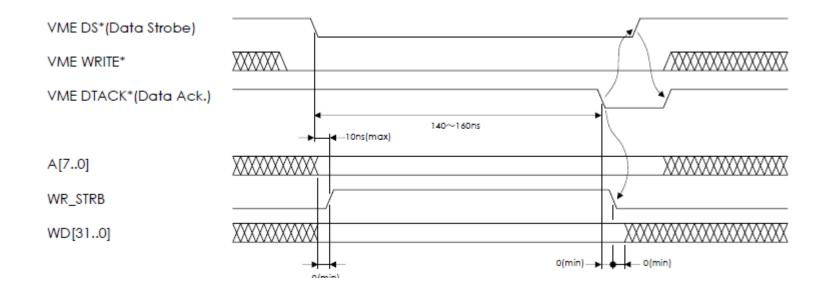

#### Accessing VME/CAMAC buses (for LUPO)

Data are read from WD at the transition timing of WE\_STRB '1' to '0'

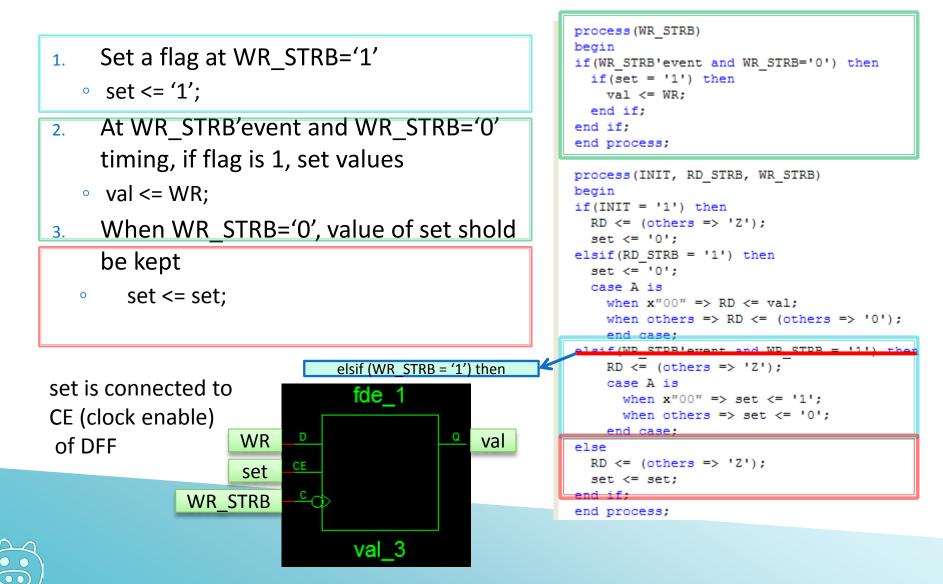

## Example of data readout (LUPO)

elsif (WR STRB = '1') then

- By using when statement, VME

Address (CAMAC AF) is selected

- During RD\_STRB='1', data must be latched on RD

- RD <= val;

</pre>

- Other cases, RD is unconnected

- o RD <= (others => 'z');

```

process(WR STRB)

begin

if (WR STRB'event and WR STRB='0') then

if(set = '1') then

val <= WR:

end if:

end if:

end process;

process(INIT, RD STRB, WR STRB)

begin

if(INIT = '1') then

RD \ll (others => 'Z');

set <= '0';</pre>

elsif(RD STRB = '1') then

set <= '0':

case A is

when x"00" => RD <= val;</pre>

when others => RD <= (others => '0');

end case;

if (WD_STDR!event and WD_STDR = 11

RD \ll (others => 'Z');

case A is

when x"00" => set <= '1';

when others => set <= '0';

end case;

else

RD \ll (others => 'Z');

set <= set;

end if;

end process;

```

## Example of data write (LUPO)

## Make a scaler (counter)

- By using event, make a synchronous circuit

- cnt <= cnt + 1

- When data readout, data must be latched at the RD\_STRB, otherwise you get invalid values, sometimes

- If cnt value is changed during readout, it is bad

- There are skew (- 20ps) between all bits

```

entity SCRWORK is

Port ( c : in STD LOGIC;

rst : in STD LOGIC;

q : out STD LOGIC VECTOR (3 downto 0));

end SCRWORK;

architecture Behavioral of SCRWORK is

signal cnt : std logic vector(3 downto 0) := "0000";

begin

q \leq cnt;

process(rst, c)

begin

if(rst = '1') then

cnt <= (others => '0');

elsif(c'event and c='1') then

cnt <= cnt + 1;

end if:

end process;

end Behavioral:

```

#### Latching the value of Scaler (Counter)

Prepare the vector for readout

```

elsif(c'event and c='1') then

cnt <= cnt + 1;

if(f = '0') then

iq <= cnt + 1;

else

iq <= iq;

end if;

end if;

lt is not "iq <= cnt;"

If you this, you get value

of cnt - 1</pre>

```

```

entity SCRWORK is

Port ( c : in STD LOGIC;

f : in STD LOGIC;

rst : in STD LOGIC;

q : out STD LOGIC VECTOR (31 downto 0));

end SCRWORK:

architecture Behavioral of SCRWORK is

signal cnt : std logic vector(31 downto 0) := x"00000000";

signal iq : std logic vector(31 downto 0) := x"00000000";

begin

q <= iq;

process(rst, c)

begin

if(rst = '1') then

cnt <= (others => '0');

iq <= (others => '0');

elsif(c'event and c='1') then

cnt <= cnt + 1;

if(f = '0') then

iq <= cnt + 1;

else

iq <= iq;

end if;

end if:

end process;

```

end Behavioral;

### **Declare usuful libraries**

- library IEEE;

- use IEEE.STD\_LOGIC\_1164.ALL;

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

```

- use IEEE.STD\_LOGIC\_ARITH.ALL;

- use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

cnt <= cnt + 1 requires ARITH</li>

If you simulate with built in libraries such as FDCE, you have to uncomment like this

-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. library UNISIM; use UNISIM.VComponents.all;

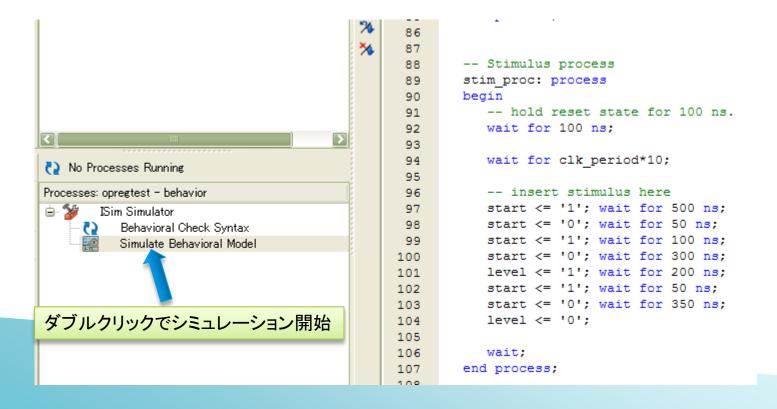

#### **Do simulation**

#### Create the Test Bench

| 📑 View: 💿 🄯 Implementation 🔿 🎆 Simulat                                                                                                                                                                                                                                                                                                                                                                                               | 🚾 New Source Wizard                                                                                                                                                                                                                                                                                                                             |                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Hierarchy<br>VLUPODAQMaster<br>Carteria xc3s500e-4pq208<br>Carteria Correctional (OPREG.vho                                                                                                                                                                                                                                                                                                                                          | Select Source Type<br>Select source type, file name and its location.                                                                                                                                                                                                                                                                           |                                                                            |

| OPREG - Behavioral (OPREG.vhd     VLUPODAQMaster - Behavior     div10mmap - DIVIDER - Behavior     div10kmap - DIVIDER - Behavior     div10kmap - DIVIDER - Behavior     div1kmap - DIVIDER - Behavior     STRBMAP - DIVIM - Behavior     FVALPWID - FVAL - Behavior     FVALINTDL - FVAL - Behavior     FVALINTEC - FVAL - Behavior     SCRMAP0 - SCALER - Behavior     SCRMAP1 - SCALER - Behavior     SCRMAP2 - SCALER - Behavior | <ul> <li>ChipScope Definition and Connection File</li> <li>Implementation Constraints File</li> <li>IP (CORE Generator &amp; Architecture Wizard)</li> <li>MEM File</li> <li>Schematic</li> <li>User Document</li> <li>Verilog Module</li> <li>Verilog Test Fixture</li> <li>VHDL Module</li> <li>VHDL Library</li> <li>VHDL Package</li> </ul> | File name:<br>Lo <u>c</u> ation:<br>s¥DAQ¥FPGA¥LUPO¥Project¥VLUPODAQMaster |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                 | Add to project                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | More Info                                                                                                                                                                                                                                                                                                                                       | Next > Cancel                                                              |

#### Set initial values

```

--Inputs

signal clk : std logic := '0';

signal start : std logic := '0';

Implementation

signal level : std logic := '0';

signal width : std logic vector(15 downto 0) := (others => '0');

Simulation

signal width : std logic vector(15 downto 0) := x"000a";

Switch

--Outputs

signal q : std logic;

-- Clock period definitions

Design

↔ □ ♬

constant clk period : time := 10 ns;

View: 🔘 🔯 Implementation 💿 🎆 Simulation

constant clk period : time := 20 ns;

Behavioral.

æ

Hierarchy.

6

🝯 VLUPODAQMaster

🖮 🋄 xc3s500e-4pq208

🐘 VLUPODAQMaster - Behavioral (VLUPODAQMa

÷

2

a

🖮 😘 opregtest - behavior (opregtest.vhd)

🐘 uut - OPREG - Behavioral (OPREG.vhd)

A

23

%

1

3

×

```

### Write like this

clock part are generated automatically

wait for 100ns; means 100ns passing

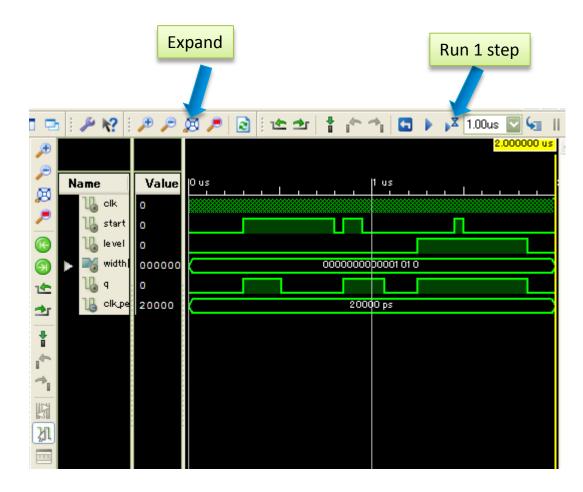

### ISim

# Download firmware to LUPO/GTO

#### Generate Programming File

- bit file is generated

- Configure Target Device

- Launch iMPACT

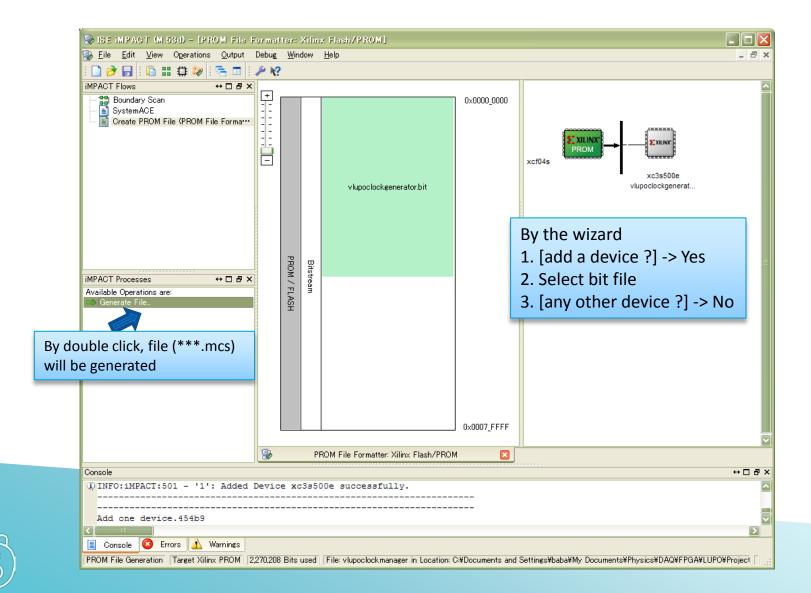

- Make file for the flash memory from bit file

- Load into FPGA

First step, PROM = Flash Memory file

| 😺 Welcome to IMPACT 🛛 🔀                                             |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|--|--|--|--|--|--|--|

| Please select an action from the list below                         |  |  |  |  |  |  |  |

| O Configure devices using Boundary-Scan (JTAG)                      |  |  |  |  |  |  |  |

| Automatically connect to a cable and identify Boundary-Scan chain 💌 |  |  |  |  |  |  |  |

| Prepare a PROM File                                                 |  |  |  |  |  |  |  |

| O Prepare a System ACE File                                         |  |  |  |  |  |  |  |

| O Prepare a Boundary-Scan File                                      |  |  |  |  |  |  |  |

| SVF 🔍                                                               |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

| OK                                                                  |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |  |

# Setting of PROM file

|                                                                                                                                                                                                                                                                                                                 |                      | GTO case          | , it is xcf02s       |             |                                                                   |          |                         |                  |                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|----------------------|-------------|-------------------------------------------------------------------|----------|-------------------------|------------------|-------------------|

| 😵 PROM File Formatter                                                                                                                                                                                                                                                                                           |                      |                   | ,                    | -           |                                                                   |          |                         |                  | ×                 |

| Step 1. Selec                                                                                                                                                                                                                                                                                                   | t Storage T          | arget             | St 2.                | Ado         | d Storage Device(s)                                               |          | Step 3.                 |                  | Enter Data        |

| Storage Device Type :                                                                                                                                                                                                                                                                                           |                      | Choose            | xcf04s and A         | Add         | Platform Flash                                                    |          | ieneral File Detai      |                  | Value             |

| Xilinx Flash/PROM                                                                                                                                                                                                                                                                                               |                      |                   | Dey (bits)           | -           | xct04s [4 M]                                                      |          | Checksum Fill<br>Value  | FF               |                   |

| Grim Spartan3AN<br>Grim SPI Flash                                                                                                                                                                                                                                                                               |                      |                   | Add Storage          | Device      | Remove Storage Device                                             |          | Output File Name        | vlupoclockman    | ager              |

| Configure Single FPGA<br>Configure MultiBoot FP                                                                                                                                                                                                                                                                 | GA                   |                   | xcf04s               | [4 M]       |                                                                   |          | Output File<br>Location | O/Project/VLUP   | OClockGenerator 📂 |

| Configure Single FPGA                                                                                                                                                                                                                                                                                           | GA                   |                   |                      |             |                                                                   |          | Flash/PROM F            | ile Property     | Value             |

| Configure from Parallel                                                                                                                                                                                                                                                                                         | ed PROMs             |                   |                      |             |                                                                   |          | File Format             |                  | MCS 🔽             |

| Generier araller Koh                                                                                                                                                                                                                                                                                            |                      |                   |                      |             |                                                                   |          | Add Non-Configura       | tion Data Files  | No                |

|                                                                                                                                                                                                                                                                                                                 | Choose               | Xilinx Flash      | n/PROM               |             |                                                                   |          |                         |                  |                   |

|                                                                                                                                                                                                                                                                                                                 | and pres             | SS                |                      |             |                                                                   |          |                         |                  |                   |

|                                                                                                                                                                                                                                                                                                                 |                      |                   | Auto Selec           | t PROM      |                                                                   |          |                         |                  |                   |

| Description:                                                                                                                                                                                                                                                                                                    |                      |                   |                      |             |                                                                   |          |                         |                  |                   |

| In this step, you will enter information to assist in setting up and generating a PROM file for the targeted storage device and mode.  • Checksum Fill Value: When data is insufficient to fill the entire memory of a PROM, the value specified here is used to calculate the checksum of the unused portions. |                      |                   |                      |             |                                                                   |          |                         |                  |                   |

| • Output File Name: T<br>• Output File Location                                                                                                                                                                                                                                                                 | his allows you to sp | ecify the base n  | ame of the file to v | which your  | PROM data will be written                                         | to calcu | iate the checkSUM o     | r are unused por |                   |

| <ul> <li>File Format: PROM file</li> </ul>                                                                                                                                                                                                                                                                      | es can be generate   | ed in an yn umber | of industry standa   | rd formats. | Depending on the PROM file fo<br>hat utilize IEEE Std 1532. Third |          |                         |                  |                   |

|                                                                                                                                                                                                                                                                                                                 |                      |                   |                      |             |                                                                   |          | Ōĸ                      | <u>C</u> an c    | el Help           |

#### **Generate PROM file**

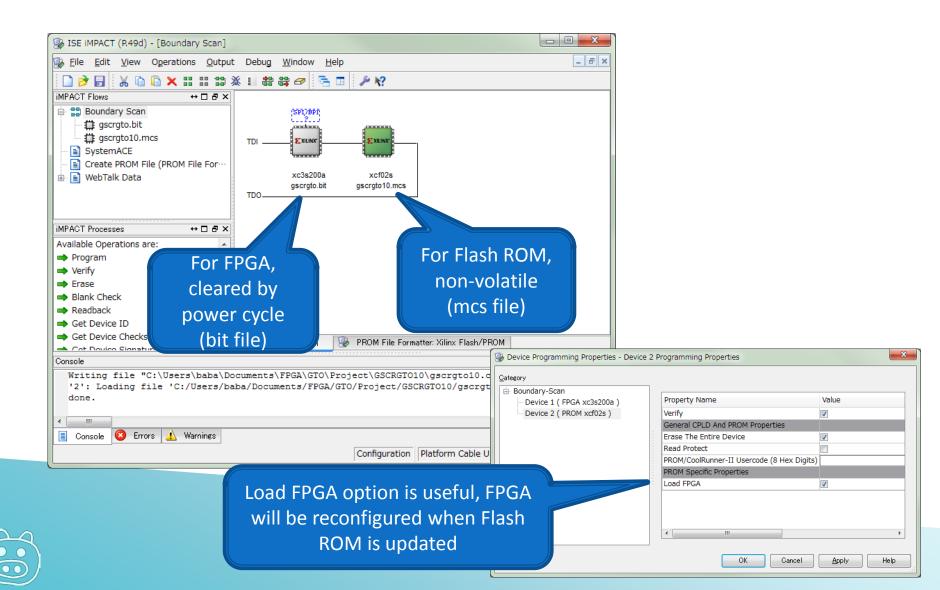

### **Download firmware**

#### Ex. mistake case, conv\_std\_logic\_vector

- Converting to the numerical value of 5000000 to the 24bits vector

- conv\_std\_logic\_vector(5000000, 24)

• Good

- conv\_std\_logic\_vector(24, 500000)

- Converting the numerical value of 24 to the 500000bits vector

- Synthesize take so long time

### "downto" and "to"

- signal a : std\_logic\_vector(3 downto 0) := "3210"

- Using vector, downto is usual

- Writing initial value with "bit", it is common that the most right position is 0-th bit

- type ARINT is array(3 downto 0) of integer;

- constant b : ARINT := (0,1,2,3);

- It will be b(0)=3, b(1)=2, b(2)=1,b(3)=0

- type ARINT is array(0 to 3) of integer;

- constant b : ARINT := (0,1,2,3);

- b(0)=0, b(1)=1, b(2)=2,b(3)=3

- Depending on custom,,, when array, to is easier to understand

# If you find a warning of black box

- attribute box\_type : string;

- attribute box\_type of FDCE : component is "black\_box";

- Warning will be solved

```

COMPONENT FDCE

generic (INIT : bit := '1');

PORT(

Q : OUT std_logic;

C : IN std_logic;

CE : IN std_logic;

CLR : IN std_logic;

D : IN std_logic;;

END COMPONENT;

attribute box_type : string;

attribute box_type of FDCE : component is "black box";

```

Or, you don't need to declare COMPONENT that are defined in Xilinx Library, simply uncomment these lines

> -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. library UNISIM; use UNISIM.VComponents.all;

# Using LVDS

#### IBUFDS Input

- For input case, write DIFF\_TERM = TRUE

- Terminator is installed

```

INST "LVDSn*" DIFF_TERM = "TRUE";

INST "LVDSp*" DIFF_TERM = "TRUE";

```

OBUFDS Output

```

component OBUFDS

port (

I : in STD_LOGIC;

O : out STD_LOGIC;

OB : out STD_LOGIC);

end component;

```

```

LVDSOUT_MAPgene : for i in 0 to 15 generate

LVDSOUT_MAP : OBUFDS

port map (

I => LVDSio(i),

0 => LVDSp(i),

OB => LVDSn(i));

end generate;

```

signal LVDSio : std logic vector(15 downto 0);

### GCLK and BUFG

- Inputs assigned to GCLK can be used as a Clock (having small Skew and Delay)

- IPO and LVDSClockp/n

- By connecting BUFG, other inputs are also can be used as a Clock (it will be the Clock of many other circuit components)

- Basically, it is automatically connected at the Place & Route

- Following declaration is necessary in UCF

NET "WR\_STRB" CLOCK\_DEDICATED\_ROUTE = FALSE;

- With larger circuit, please check "Place & Route Report"

- In case of Local (not BUFGMUX) and Skew is large, the wiring tuning with PlanAhead is necessary

| + | +               | +             | +      | ++     | +            | +             |

|---|-----------------|---------------|--------|--------|--------------|---------------|

| Ļ | Clock Net       | Resource      | Locked | Fanout | Net Skew(ns) | Max Delay(ns) |

| į | IP_2_IBUF       | BUFGMUX_X1Y1  | No     | 32     | 0.023        | 0.168         |

| ļ | div1kmap/iq     | BUFGMUX_X2Y0  | No     | 32     | 0.017        | 0.165         |

| i | trg             | BUFGMUX_X2Y1  | No     | 48     | 0.043        | 0.165         |

| I | CLOCK_BUFGP     | BUFGMUX_X2Y11 | No     | 180    | 0.086        | 0.203         |

| i | div10kmap/iq    | BUFGMUX_X1Y0  | No     | 32     | 0.019        | 0.164         |

| ļ | IP_1_IBUF       | BUFGMUX_X1Y11 | No     | 32     | 0.018        | 0.168         |

| l | rawtrg          | BUFGMUX_X3Y8  | No     | 33     | 0.033        | 0.092         |

| ļ | IP_3_IBUF       | BUFGMUX_X0Y8  | No     | 32     | 0.021        | 0.113         |

| į | div10mmap/iq    | BUFGMUX_X3Y4  | No     | 32     | 0.013        | 0.085         |

| ļ | IP_0_IBUF       | BUFGMUX_X1Y10 | No     | 32     | 0.018        | 0.168         |

| ļ | wrstrbg         | BUFGMUX_X3Y9  | No     | 76     | 0.063        | 0.122         |

| i | Inst_TRGVET0/q1 | Local         |        | 5      | 0.000        | 1.744         |

| + |                 |               |        |        |              | +             |