## FPGA Lecture for LUPO and GTO Vol.3 Hidetada baba

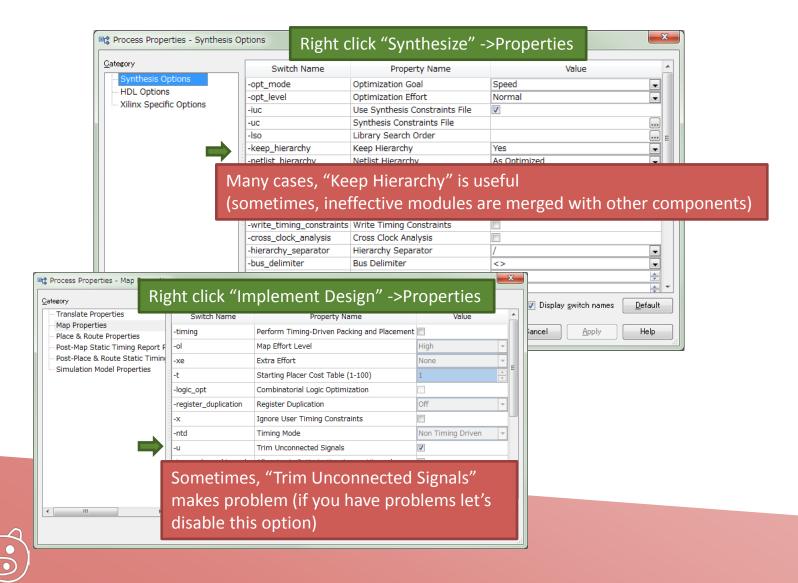

#### **Important options**

## Simulation with Delay 1/3

#### We can simulate the delay of components and wires in FPGA

| Pight c           | lick "Implement Design"                            | ->Properties                                      |             |            | xc3s200a-4vq100                            | ▲   15  m   m | 30<br>31<br>32<br>33<br>34 | Uncomment t<br>arithmetic<br>USE ieee.num |

|-------------------|----------------------------------------------------|---------------------------------------------------|-------------|------------|--------------------------------------------|---------------|----------------------------|-------------------------------------------|

| Night C           | lick implement Design                              |                                                   |             | <b>621</b> | SCLKINST - DIVIDERWID8b - Behaviora        | ×             | 35<br>36                   | ENTITY dltest4<br>END dltest4;            |

| Process Properti  | es - Simulation Moder Properties                   |                                                   | ×           |            | 🖃 🙀 Inst_DLCHAIN - DLCHAIN - Behavioral (  |               | 37                         |                                           |

|                   |                                                    |                                                   |             |            | RSTMAP - SPULSE - Behavioral (SPU          | 26            | 38                         | ARCHITECTURE 1                            |

| Switch Name       | Property Name                                      | Value                                             |             |            | 🖃 🔛 InstDLCHAING - DLCHAIN - Behavioral    | *             | 39<br>40                   | Compone                                   |

|                   | Simulation Model Target                            | /HDL                                              | -           |            | RSTMAP - SPULSE - Behavioral (SPU          |               | 40                         | Compone                                   |

| S                 | -                                                  | 4                                                 |             |            | - 🛐 Inst_RS232RX - RS232RX - Behavioral (I | : 6           | 42                         | COMPONENT                                 |

| fn                | Retain Hierarchy                                   | ।<br>न                                            |             |            | - 🛐 Inst_RS232TX - RS232TX - Behavioral (I | -             | 43                         | PORT (                                    |

| mhf               |                                                    |                                                   |             |            | - 📓 Inst_GTOCOM - GTOCOM - Behavioral (    |               | 44                         | CLOCF<br>LED :                            |

| -tp               | Bring Out Global Tristate Net as a Port            |                                                   |             |            | - 🔛 IVIDERWID1K - DIVIDERWID - Behavioi    |               | 45<br>46                   | NIN :                                     |

| φ                 | -                                                  | TS_PORT                                           |             |            | 🛛 🔛 CVAL_testinst - CVAL - Behavioral (CVA |               | 47                         | NOUT                                      |

| gp                |                                                    |                                                   |             |            | CVAL_ssminst - CVAL - Behavioral (CVA      |               | 48                         | XRX :                                     |

| .ah               |                                                    | SR PORT                                           |             | •          | CTOCOMINET CTOCOM Babaviaral (             |               | 49                         | XTX :                                     |

| tb                |                                                    |                                                   |             |            |                                            |               | 50<br>51                   | );<br>END COMPON                          |

| ti                |                                                    |                                                   |             | P 🖸        | No Processes Running                       |               | 52                         | END CONFOR                                |

| -                 | ··-······                                          |                                                   |             | Pro        | ocesses: DLGTO - Behavioral                |               | 53                         |                                           |

| inserc_pp_buriers | Other NETGEN Command Line Options                  |                                                   |             | 91         | Generate Post-Translate Simulatio…         |               | 54                         | Inputs                                    |

| tm                | Rename Top Level Entity to                         | GIO                                               |             |            | 🖶 🍋 🔥 Map                                  |               | 55<br>56                   | signal CLOC<br>signal NIN                 |

| ar                |                                                    | Structure                                         |             | -4         | E CA Place & Route                         |               | 50                         | signal XRX                                |

|                   | Tristate On Configuration Pulse Width              | structure                                         |             |            | 🖶 🏹 🖉 Generate Post-Place & Route Stati…   |               | 58                         |                                           |

| tpw               |                                                    | .00                                               |             |            | 🛛 🍏 🛛 Analyze Post-Place & Route St…       |               | 59                         | Outputs                                   |

| rpw               |                                                    |                                                   |             |            | Generate Primetime Netlist                 |               | 60                         | signal LED                                |

| ā                 | Generate Architecture Only (No Entity Declaration) |                                                   |             |            | 🐻 Analyze Timing / Floorplan Design        |               | 61<br>62                   | signal NOUI<br>signal XTX                 |

| extid             | Output Extended Identifiers                        |                                                   |             |            | 🔯 View/Edit Routed Design (FPGA Ed…        |               | 63                         | Signal AIA                                |

| tm                | Rename Top Level Module To                         |                                                   |             |            | Analyze Power Distribution (XPow…          |               | 64                         | Clock pe                                  |

| ul                | Include 'uselib Directive in Verilog File          |                                                   |             |            | Generate Text Power Report                 |               | 65                         | constant CI                               |

| sdf_anno          |                                                    |                                                   |             |            |                                            |               | 66<br>67                   | BEGIN                                     |

| sdf_path          |                                                    | Default                                           |             |            | 🕀 🍋 Generate IBIS Model 🛛 🗉                |               | 68                         | DEGIN                                     |

| ne                | Do Not Escape Signal and Instance Names in Netlist |                                                   |             |            | Back-annotate Pin Locations                |               | 69                         | Instantia                                 |

| ism               | Include SIMPRIM Models in Verilog File             |                                                   |             |            | 😲 🕜 Generate Programming File              |               | 70                         | uut: DLGTO                                |

| insert_glbl       | Automatically Insert glbl Module in the Netlist    | 2                                                 |             |            | Source Configure Target Device             |               | 71                         | CLOC                                      |

|                   | Proper                                             | y display level Advanced 💌 🛛 Display switch names | Default Ger | iera       | te Post-Place & Route                      | Sin           | nula                       | ation Mo                                  |

|                   |                                                    | OK Cancel Apply                                   | Help        | Console    |                                            |               |                            |                                           |

ISE Project Navigator (0.87xd) - C:¥Users¥baba¥Documents¥FPGA¥GTO¥Project¥DLGTO¥E

] 🖻 🖉 🗟 🐰 🗅 🗋 🗙 🗠 여기 🗙 🖉 🖉 🖉 🔁 🗌

⇔⊡₽× 48

.

10 30 -- simulation

USE ieee.std 1

28 LIBRARY ieee;

26

27 **N**

29

File Edit View Project Source Process Tools Window Layout Help

Design

J Hierarchy

DLGTO

📑 View: 💿 🄯 Implementation 🔘 🔜 Simulation

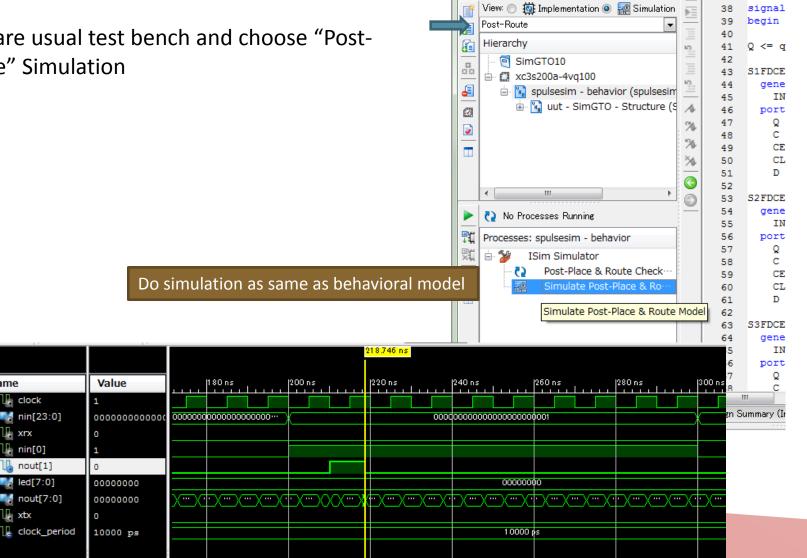

## Simulation with Delay 2/3

Prepare usual test bench and choose "Post-Route" Simulation

Design

⇔⊡₽×

archit

37

Name

clock

🕼 xrx

🕼 xtx

🔓 nin[0]

nout[1]

Ied[7:0]

📑 nin[23:0]

## Simulation with Delay 3/3

Change the delay by moving components in FPGA. (example is LUT1)

```

LUII_inst : LUII

generic map (

INIT => "10")

port map (

0 => q,

I0 => s

);

```

end Behavioral;

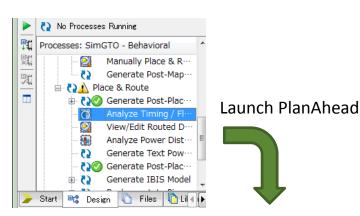

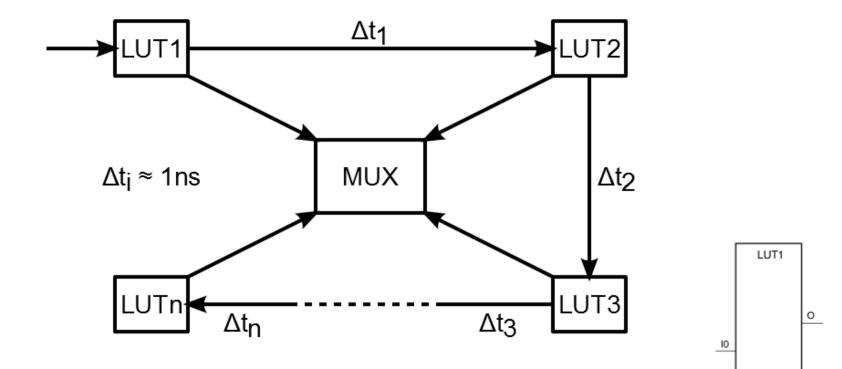

Logic delay by wiring 1/3

X9852

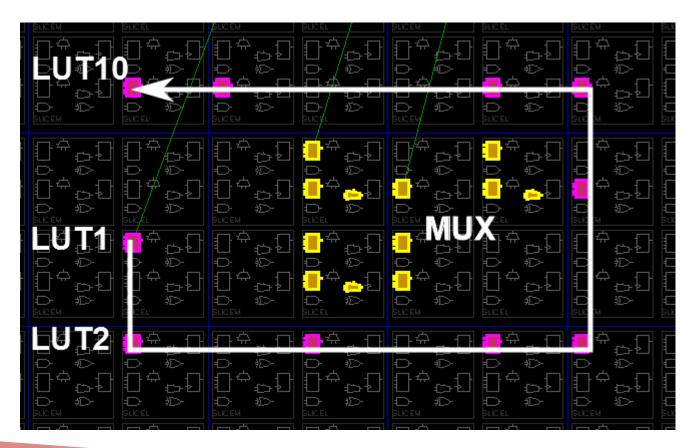

# Logic delay by wiring 2/3

#### By floor planner

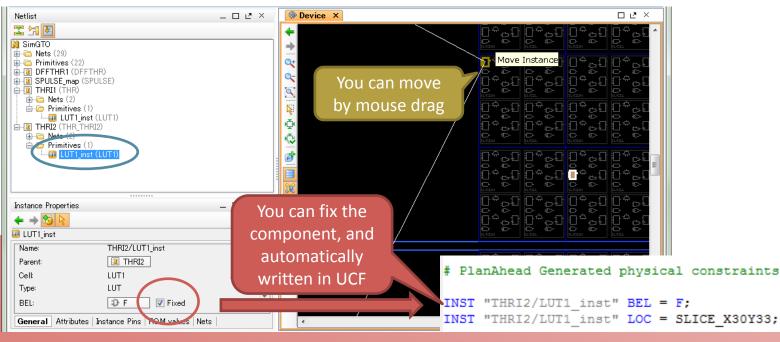

## Logic delay by wiring 3/3

#### Example of UCF file

```

INST "Inst delay2/LUT1 inst" BEL = G;

INST "Inst delay2/LUT1 inst" LOC = SLICE_X7Y8;

INST "Inst delay2/LUT2 inst" BEL = G;

INST "Inst delay2/LUT2 inst" LOC = SLICE X7Y7;

INST "Inst delay2/LUT3 inst" BEL = G;

INST "Inst delay2/LUT3 inst" LOC = SLICE X9Y7;

INST "Inst delay2/LUT4 inst" BEL = G;

INST "Inst delay2/LUT4 inst" LOC = SLICE X11Y7;

INST "Inst delay2/LUT5 inst" BEL = G;

INST "Inst delay2/LUT5 inst" LOC = SLICE X12Y7;

INST "Inst delay2/LUT6 inst" BEL = F;

INST "Inst delay2/LUT6 inst" LOC = SLICE X12Y9;

INST "Inst delay2/LUT7 inst" BEL = F;

INST "Inst delay2/LUT7 inst" LOC = SLICE X12Y10;

INST "Inst delay2/LUT8 inst" BEL = F;

INST "Inst delay2/LUT8 inst" LOC = SLICE X11Y10;

INST "Inst delay2/LUT9 inst" BEL = F;

INST "Inst delay2/LUT9 inst" LOC = SLICE X8Y10;

INST "Inst delay2/LUT10 inst" BEL = F;

INST "Inst delay2/LUT10 inst" LOC = SLICE X7Y10;

```

Some times, multiple LUTs packed into 1LUT. To avoid this, hand-write constraints are required before floor planner.